二維材料過渡金屬硫化物元件製程及其積層三維整合技術

2D Device Fabrication and Technique on Monolithic 3D Integration of 2D Transition Metal Dichalcogenides

有別於傳統矽基電晶體為主的半導體產業應用,原子層厚度的二維半導體材料為主的發展也越來越被重視。但由於此技術的發展深深地被材料與金屬電極介面所影響,如能有效地克服接觸電阻所造成的電子傳輸問題,如此便能提供產業實現超高功效電子元件的應用。本文介紹本實驗室所發展出的低接觸電阻二維材料過渡金屬硫化物元件和呈現二維材料積層三維整合技術,如此提供了整合二維材料元件與當今成熟的半導體產線可行的製程方向,可望加速二維材料元件的量產以及其三維異質整合元件。

Different from the traditional silicon-based semiconductor industry applications, the development of 2D semiconductor materials with an atomic layer thickness has also been paid more and more attention. However, since the development of this technology is deeply affected by the interface between the material and the metal electrode, it is desirable to solve the contact resistance issue, so as to the industry with the possible application of ultra-high-efficiency electronic components. This article introduces the strategy for 2D electronics with low contact resistance developed by our laboratory and the technique on monolithic 3D integration of the 2D semiconductor transistor. The proposed fabrication process can provide a feasible way to achieve the 3D integration with the existing semiconductor manufacturing process. This process is promising to achieve a large-scale fabrication of 2D material transistors and boost up the further development of monolithic 3D integrated circuits.

一、前言

在傳統半導體產業應用中,大多數的電晶體都是以矽為基礎材料所製作而成的,過去幾十年來,科技的發展一直在朝著縮小電晶體尺寸的目標而努力著,為的就是盡可能地達成符合摩爾定律的標準,此定律則指出晶片上每單位面積的電晶體數量及其性能大約每兩年須提升一倍。然而,由於更多的積體電路被塞入一個小區域中會使得元件在操作時會產生大量的熱能,進而影響效能的表現,另一方面,電晶體的尺寸也無法無限制地持續縮小,最終將達到其物理極限而無法滿足長久以來遵循的摩爾定律。因此,適當的新穎材料的引入將能夠提供與矽相同甚至更好的性能。最近,極具潛力的材料已成為許多科學研究的主題,例如一維的奈米碳管 (carbon nanotube, CNT)、二維的石墨烯 (graphene) 及過渡金屬硫化物 (transition metal dichalcogenide, TMD) 等都是可以用來替代矽並繼續遵循摩爾定律的傑出候選者。

對於僅有原子層厚度的二維材料來說,在元件的製作技術發展中,必須謹慎地考量到材料與金屬電極介面接合所造成的接觸問題,因此若能提供一些能有效地克服接觸電阻所造成的電子傳輸問題,便能提供產業實現超高功效電子元件非常具有潛力的應用。此外,對於二維材料元件在未來是否能實際應用於當前的半導體製程產線上與其產品的應用,則需考慮兩種異質材料特性與元件製造過程中的相容性,必須確保元件的特性在經歷過多道製程後,其特性仍不會被改變太多。因此,二維材料與半導體元件之積層式三維整合製程技術將能夠滿足後端製程整合的需求,進而讓下層元件可維持其應有的效能,並提供整合二維材料元件與當今成熟的半導體產線可行的製程方向,可望加速二維材料元件的量產以及其三維異質整合元件。

二、二維材料過渡金屬硫化物元件製程技術

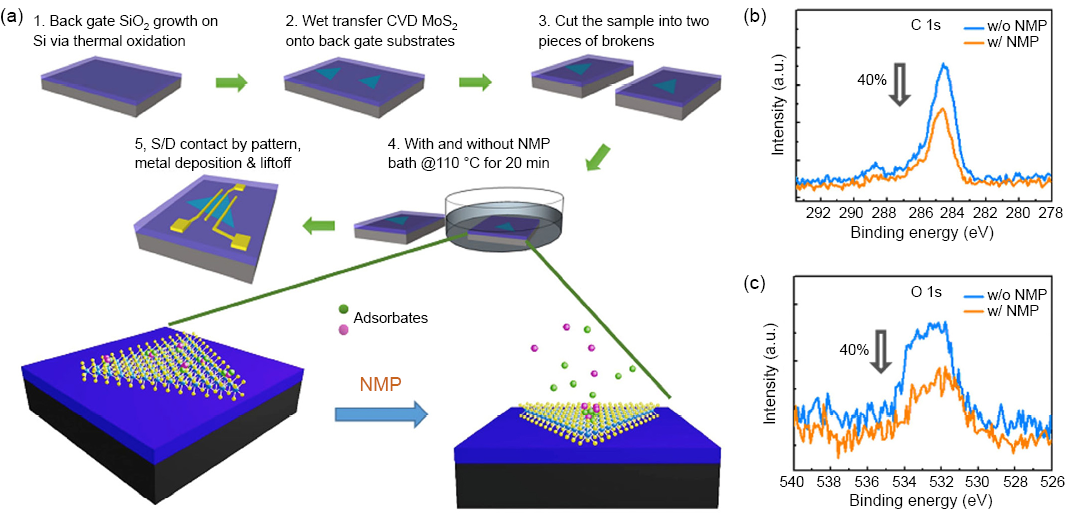

為了提供能有效地避免接觸電阻所造成的電子傳輸問題之解方,並且使二維材料與當今半導體製程整合上具有可行的方向,以期加速二維材料元件的量產,並促進將來更多功能之二維材料三維整合元件之開發,本實驗室發展一套有效提升二維材料電晶體效能的製程,且可與現今半導體後段製程相匹配。目前二維材料元件製程技術中,許多議題等待得到更有效的解決方案,其中針對材料與電極介面之間所普遍面臨到的蕭特基能障 (Schottky barrier) 問題,更是迫切需要被解決來達成電性傳輸特性上的突破。其中在二維材料轉置於特定基板的製程中,常常會塗佈光阻劑 (例如聚甲基丙烯酸甲酯 poly (methyl methacrylate), PMMA) 作為保護層來避免過程中造成材料的破壞。然而,若此光阻劑保護層未能完全地被清除乾淨,將使得介面間存在一層嚴重影響接觸電阻 (RC) 的絕緣層。因此我們在二維材料轉置後,將先行採用 N-甲基吡咯烷酮 (n-methyl-2-pyrrolidone, NMP) 溶劑進行材料表面的清潔,元件的製作流程如圖 1(a) 所示(1)。藉由上述的方式處理過後,如此便能有效地去除殘留的光阻劑以及附著於材料表面的雜質,透過量測轉移到 Au 基板上的單層 MoS2 的 X 射線光電子能譜 (X-ray photoelectron spectroscopy, XPS) 可以清楚觀察到,由碳的 1s 軌域 (C 1s) 特徵峰的數據顯示,在經過 NMP 清洗後的樣品中碳含量降低了 40%。而根據氧的 1s 軌域 (O 1s) 特徵峰的數據顯示,同樣經過 NMP 清洗後氧含量也降低了 40%,分別如圖 1(b) 及 (c) 所示。(1)

圖 1. (a) 元件製作流程示意圖。將 CVD 成長的單層 MoS2 利用濕式轉移方式置於目標基板後,先經由丙酮、IPA及NMP清洗過後,再利用電子束微影製程製作出電極。放大的插圖顯示了由 NMP 清潔後能有效去除材料表面的附著物。(b) 由 MoS2 轉移到 Au 基板上的 XPS 量測中 C 1s 特徵峰的數據顯示,在經過 NMP 清洗後的樣品中碳含量降低了約 40%。(c) 根據 O 1s 特徵峰的數據顯示,同樣經過 NMP 清洗後氧含量也降低了約 40%。(1)

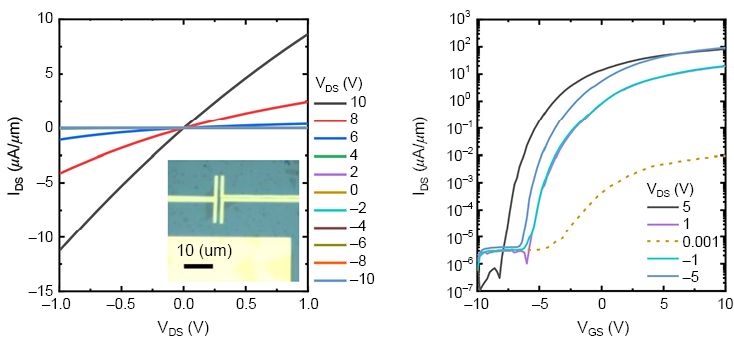

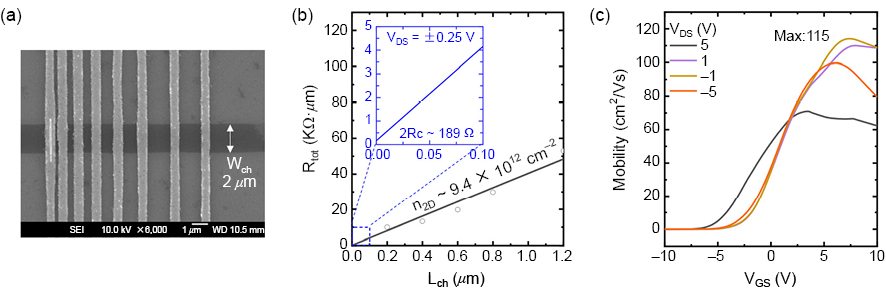

此清潔程序不僅維持了二維材料本質的特性不至於造成過度的侵蝕破壞,也大幅地提升了元件的電子傳輸特性。圖 2(a) 顯示了在電極為鈦/鎳 (Ti/Ni) 的單層二硫化鉬 (molybdenum disulfide, MoS2) 場效應電晶體 (field-effect transistor, FET) 元件中,其電流可達到 12 μA·μm–1 (通道長度約為 400 nm);接觸電阻約為 15 kΩ·μm;平均的電流開關比 (on-off ratio) 可達到 108 的數量級,如圖 2(b) 所示。此外,藉由改良元件電極所使用的材料,我們發現使用鉍/金 (Bi/Au) 作為電極可以使材料與金屬之間的接觸電阻 (RC) 得到突破性的改善,圖 3(a) 呈現了元件的掃描式電子顯微鏡 (scanning electron microscopy, SEM) 影像,此元件所使用的帶狀單層 MoS2 是刻意經過蝕刻製程所製作出來的,目的是為了避免當我們為了要比較不同通道長度所形成的電子傳輸特性時,因為通道尺寸上的不一致所造成比較上的誤差。因此,從電性量測結果分析電阻值隨不同通道長度所呈現的關係圖中可以看出,在元件操作於偏壓 VDS = 0.25 V 時,其電阻值能夠降低到約 100 Ω·μm,如圖 3(b) 所示;而元件的場效應載子遷移率 (field-effect mobility) 可達到 115 cm2·V–1·S–1,如圖 3(c) 所示。此效果主要歸因於半金屬態的鉍與半導體材料之間雖然會形成金屬引起的間隙能態 (metal-induced gap states, MIGS),然而此間隙能態卻在鉍與過渡金屬硫化物介面間能有效地被抑制並形成簡併態 (degenerate states)。(2)

圖 2. (a) IDS-VDS 電子傳輸特性顯示了線性的歐姆接觸特性,縮圖為元件的光學影像圖,其電極材料為鈦/鎳 (Ti/Ni)。(b) IDS-VGS 電子傳輸特性可以觀察到在元件操作於偏壓 VDS = –5 V 時能夠達到大約 108 級距的電流開關比。

圖 3. (a)寬度約為 2 μm 的單層 MoS2 元件的掃描式電子顯微鏡 (scanning electron microscope, SEM) 影像。(b) 由電性量測結果分析電阻值隨不同通道長度所呈現的關係圖中可以看出,在元件操作於偏壓 VDS = 0.25 V 時,其接觸電阻可以降低到約 100 Ω·μm。(c)元件的場效應載子遷移率在操作於偏壓 VDS = –1 V時可達到 115 cm2·V–1·S–1。

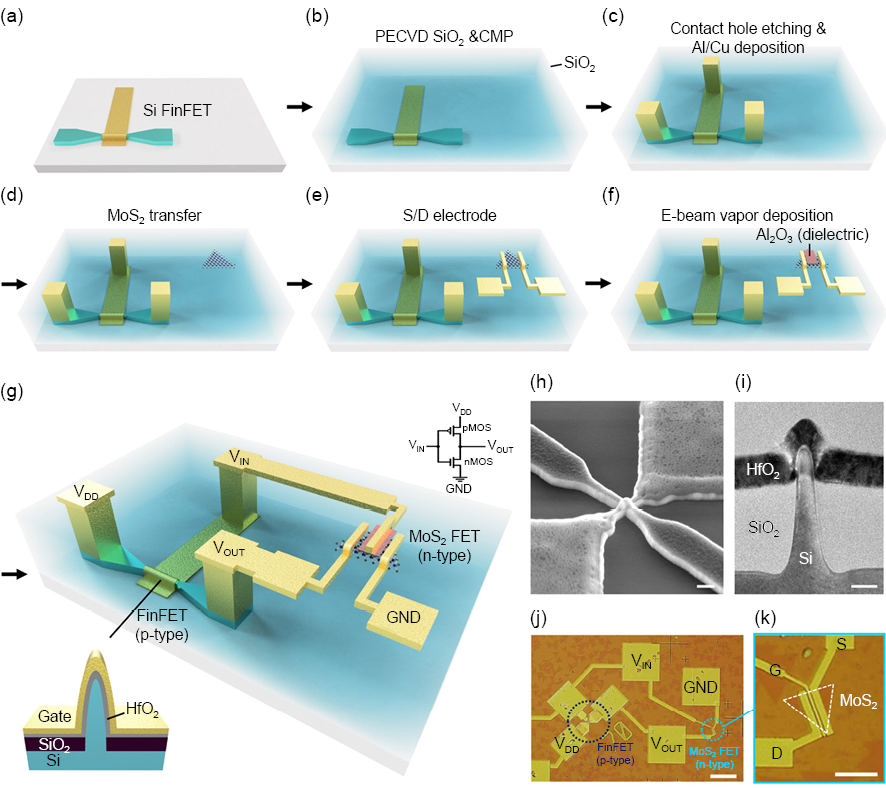

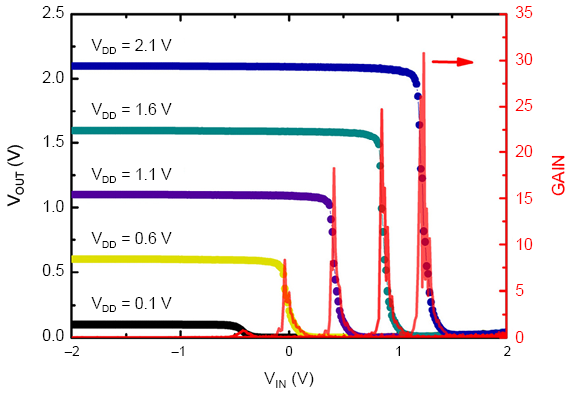

三、積層三維堆疊製程技術

整合上述所介紹的二維材料元件製程,我們進一步提出可相容於當今半導體後段製程的積層式三維整合技術,將 n 型二維半導體材料 MoS2 與 p 型半導體矽之鰭式電晶體 (FinFET) 整合成三維空間的互補式金屬-氧化物-半導體 (complementary metal-oxide-semiconductor, CMOS) 反相器,其元件特性相較於目前鰭式電晶體所組成的反相器,在諸如電壓增益與功率損耗的表現上,將具有非常高的競爭力;並且可進一步與目前半導體工業普遍所使用的以矽為基礎的電子元件進行相互整合。若以 n 型半導體 MoS2 為例,現今絕大部分的二維材料所需之晶體合成溫度都較高,因此難以將現成的元件連同晶片放入腔體直接成長二維材料,然而,透過我們所發展的技術,以濕式轉置技術的方式將單層 MoS2 材料放置於下層已製備完成的 p 型矽之鰭式電晶體上,我們在轉置前先旋轉塗佈一層四乙氧基矽烷 (tetraethyl orthosilicate, TEOS) 於矽之鰭式電晶體基板上,再以電漿化學氣相沉積 (plasma enhanced chemical vapor deposition, PECVD) 的方式將 TEOS 轉換為二氧化矽 (SiO2) 以作為絕緣的介電層,接著再以化學機械拋光法 (chemical mechanical polishing, CMP) 來減薄二氧化矽介電層的厚度;將材料轉置後利用接觸穿孔蝕刻法將二氧化矽層穿孔並鍍上金屬使下層矽之鰭式電晶體之電極可以延伸至 TEOS 表面,接著進行如同前段所述的方式,從轉置到鍍上源極 (source) 和汲極 (drain) 電極之 MoS2 電晶體製程,即可完成積層式三維整合之 CMOS 反相器的元件,詳細的製作流程如圖 4(a) 到 (g) 所示。圖 4(h)、(i) 分別顯示了元件側視的 SEM 影像及元件橫截面的穿透式電子顯微鏡 (transmission electron microscopy, TEM) 影像。圖 4(j) 呈現了三維空間的 CMOS 反相器上視圖的光學顯微鏡影像,其中淡藍色虛線圓圈所放大的影像如圖 4(k) 所示。最後,由圖五可以看出我們所製作的 3D Si-MoS2 CMOS 反相器在操作的電源供應電壓 (VDD) 從 0.1 V 至 2.1 V 條件下所呈現的電壓轉換輸出特性具有不錯的表現,其中紅色曲線的峰值代表了在不同 VDD 下所對應的電壓增益值。(3)

圖 4. 3D Si-MoS2 CMOS 反相器及其製程流程的示意圖。(a) 在 SiO2/Si 基板上完成的 Si FinFET。(b) 利用 PECVD 沉積 SiO2 以在 FinFET 上創造中間層以進行鈍化,然後進行化學機械拋光使 SiO2 層變薄和變平坦。(c) 藉由使用接觸孔蝕刻和電子束氣相沉積來構建層間通孔 (monolithic intertier vias, MIV)。(d) 在 SiO2 層上轉移單層 MoS2。(e)使用電子束微影和電子束氣相沉積製造連接到 MoS2 的源極/汲極電極。(f) 電子束氣相沉積 Al2O3 介電質作為 MoS2 上的閘極電極。(g) 利用垂直積體化的 p 型通道 Si FinFET 和 n 型通道單層 MoS2 電晶體所製造的 CMOS 反相器的示意圖。左下插圖則代表 Si FinFET 的橫截面結構示意圖。(h) Si FinFET 的 SEM 影像。比例尺為 100 μm。(i) TEM影像顯示 Si FinFET 的橫截面。比例尺為 25 nm。(j) 3D CMOS 反相器上視圖的光學圖像。比例尺為 100 μm。(k) 淡藍色虛線圓圈的放大影像。比例尺為 10 μm。(3)

圖 5. 3D Si-MoS2 CMOS 反相器在操作的電源供應電壓 VDD 從 0.1 V 至 2.1 V 條件下的電壓轉換輸出特性,其中紅色曲線的峰值代表了在不同 VDD 下所對應的電壓增益。(3)

四、結論

二維材料元件製程在材料轉置後先行利用 NMP 溶劑做前處理清洗並蒸鍍特定金屬電極後,能有效地提升元件的電子傳輸特性。若將二維材料元件與目前成熟的半導體製程互相整合,在整個後段製程各部件所經歷的溫度都不超過 180 °C 的情況下,將可以滿足後段製程對於製程溫度嚴格的規範,也就是底層的 Si FinFET 之元件特性不會因上層二維材料元件的製備過程而劣化,進而實現與現今半導體製程相搭配的可行性。此外,整體製程皆利用目前半導體製程常用的技術,如電子束蒸鍍與化學、機械蝕刻等,因此也可有效地減少因製程技術轉換所產生的設備成本。接著利用我們所發展之二維材料元件製備技術,也能夠成功將二維材料與矽之電晶體以積層三維堆疊的方式整合出 CMOS 反相器,可以說是目前達成此種異質材料間三維整合的先驅之一,且其反相器可與目前以半導體矽之鰭式電晶體為基礎的反相器特性在電壓增益與功率耗損等方面相匹敵。證明我們所發展之二維材料元件製程與異質整合製程之技術可行性。